## **LECTURE 10**

Soo-Won Kim

swkim@korea.ac.kr

### **11. Sample-and Hold and Translinear Circuit**

- **11.1 Performance of sample-and-hold circuits**

- 11.2 MOS sample-and-hold basic

- **11.3 Examples of CMOS S/H circuits**

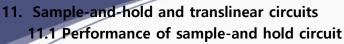

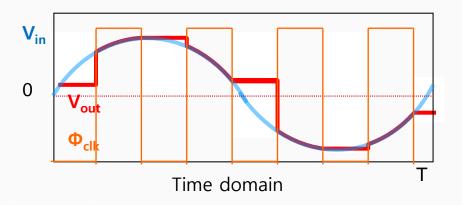

### Sample-and-hold circuit

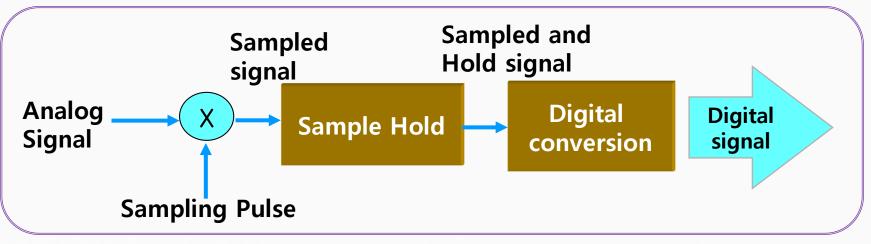

### Analog to digital converter

(1) Analog signal

(2) Sampled and Hold signal

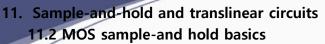

11. Sample-and-hold and translinear circuits 11.2 MOS sample-and hold basics

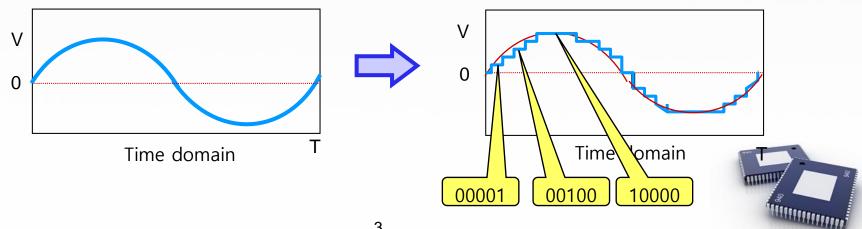

### **MOS** sample-and-hold basics

#### Operation

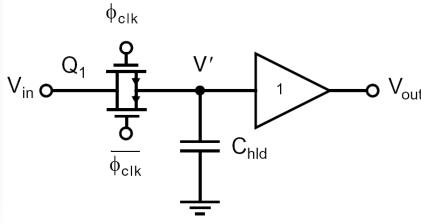

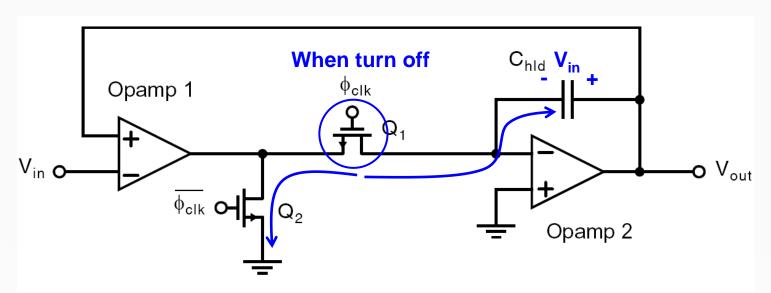

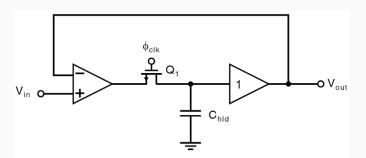

Fig. 11.3 An open-loop track and hold realized using MOS technology

- When  $\Phi_{clk}$  is closed  $rightarrow V_{out}$  samples  $V_{in}$

- When  $\Phi_{clk}$  is opened  $\longrightarrow$  Vout holds(keep value)

- Problem

- 1) Charge injection( $\Delta V'$ )  $\bigtriangleup \Delta V' = \frac{\Delta Q_{C-hld}}{C_{hld}} = -\frac{C_{ox}WL(V_{DD} V_{tn} V_{in})}{2C_{hld}}$  (11.3)

- 2) Low input impedance(lower than Amp)

### Example 11.1

### Find the hold step for $V_{in}$ equal to 1 V, 0.5V and 0.05V. Estimate the average dc offset

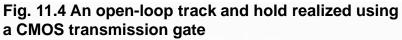

## **Reduced charge injection**

### Problem1) Charge injection

#### By transmission gate

- Reduced the charge injection

- Difficult to make up p and n transistors match Difficul Difficult to make clocks fast enough

Fig. 11.3 An open-loop track and hold realized using an n-channel switch a long with a dummy switch

#### By Dummy switch

Reduced the charge injection

Difficult to make clocks fast enough

# High input impedance

#### Problem

2) Low input impedance

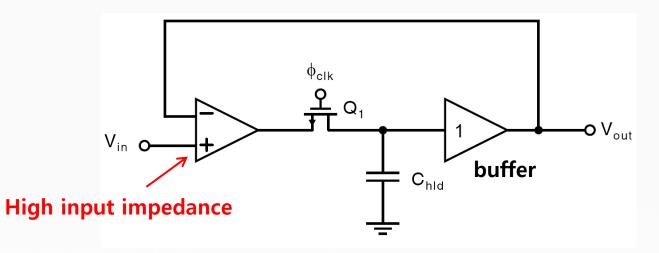

Fig. 11.7 Including an opamp in a feedback loop of a sample-and-hold to increase the input impedance

#### Advantages

- 1) High input impedance

- 2) Dc offset of buffer divided by loop gain

# High input impedance

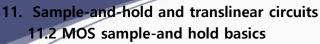

Fig. 11.7 Including an opamp in a feedback loop of a sample-and-hold to increase the input impedance

Time domain

#### Disadvantages

- 1) In hold mode, V<sub>1</sub> saturate at VDD or GND

- 2) Speed of operation can be degraded

- 3) Power consumption  $\uparrow$

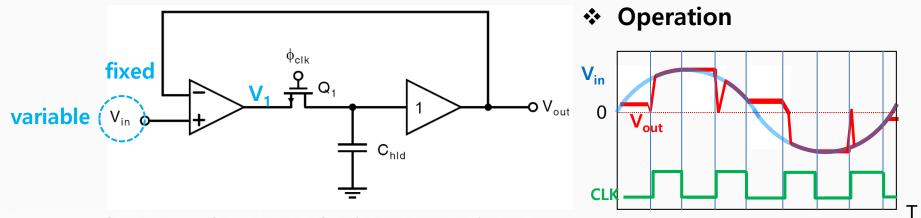

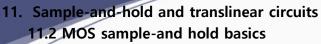

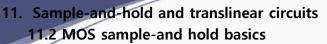

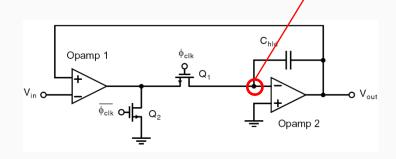

11. Sample-and-hold and translinear circuits 11.2 MOS sample-and hold basics

### **Reduced slew rate requirement**

Operation

Fig. 11.8 Adding an additional switch to the S/H of Fig. 11.7 to minimize slewing time

#### Sample-and-hold with an additional switch

- Dinimize the slewing time

- Charge injection, buffer offset

### Input signal independence

Fig. 11.9 An improved configuration for an S/H as compared to that of Fig. 11.8.

#### Improved configuration

<sup>™</sup> When hold mode, Input signal is independent  $C_{hld} \rightarrow charge$  the  $V_{in}$

### Example 11.2

# Find C<sub>hld</sub> such that the maximum error in the held voltage is limited to less than 1mV for S/H circuit (Fig. 11.7, 11.9).

$C_{ox} = 1.92 fF / (\mu m)^2$ ,  $V_{tn} = 0.8V$ ,  $(W / L)_1 = (5 / 0.8) \mu m / \mu m$ ,  $V_{DD} = 2.5V$ ,  $V_{in} = \pm 1V$

Virtual ground

Fig. 11.7 Including an opamp in a feedback loop of a sample-and-hold to increase the input impedance

$$\Delta V' = \frac{\Delta Q_{C-hld}}{C_{hld}} = -\frac{C_{ox}WL(V_{DD} - V_{tn} - V_{in})}{2C_{hld}}$$

(11.3)

$$\longrightarrow \frac{1.92f \cdot 5 \cdot 0.8(2.5 - 0.8 - (-1))}{2C_{hld}} \le 1mV$$

$\rightarrow C_{hld} \ge 10.37 \, pF$

Fig. 11.9 An improved configuration for an S/H as compared to that of Fig. 11.8.

$$\Delta V' = \frac{\Delta Q_{C-hld}}{C_{hld}} = -\frac{C_{ox}WL(V_{DD} - V_{tn})}{2C_{hld}}$$

$$\rightarrow \frac{1.92f \cdot 5 \cdot 0.8(2.5 - 0.8)}{2C_{hld}} \le 1mV$$

$$\rightarrow C_{hld} \ge 6.525 \, pF$$

C<sub>hld</sub> is reduced by 62%

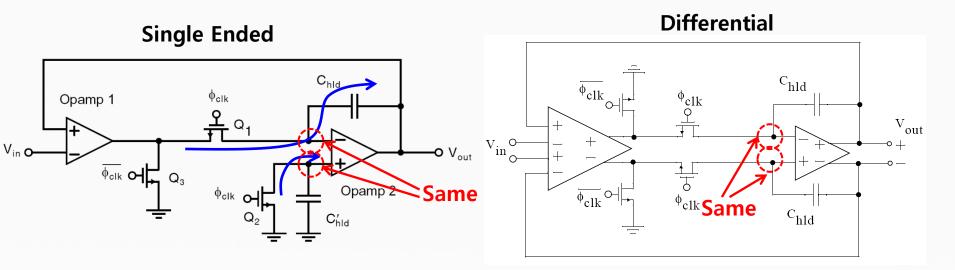

### **Reduced offset**

Fig. 11.10 An S/H similar to that of Fig. 11.9, but with clock-feedthrough cancellation circuitry added

#### **Reduced offset circuit**

Charge injected by Q1 matched by Q2 into C<sub>hld</sub> or C'<sub>hld</sub>